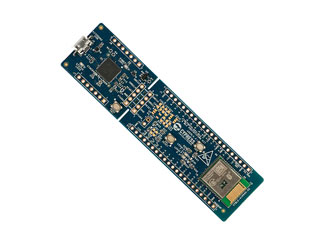

Infineon PSoC® 63 Microcontrollers

‘Connectivity Line’ MCUs are IoT game-changers

The Infineon PSoC® 63 Microcontrollers are IoT-ready MCUs which provide wireless connectivity with Bluetooth Low Energy 5 compliance. These MCUs deliver both high performance, low power, in addition to the security features that its end applications require.

Based on an ultra low-power 40-nm platform, Infineon’s PSoC® 63 MCU family is a combination of a dual-core microcontroller with low-power Flash technology and digital programmable logic. These microcontrollers also feature high-performance analog-to-digital and digital-to-analog conversion, low-power comparators, with standard communication and timing peripherals.

All PSoC® 6 MCUs feature the latest generation of industry-leading CapSense® capacitive-sensing technology, enabling modern touch and gesture-based interfaces that are robust and reliable. PSoC 6 MCU, paired with Infineon’s AIROC™ Wi-Fi, AIROC™ Bluetooth, or AIROC™ combos radio modules, is the perfect solution for secure, low-power, feature-rich IoT products.

Dual-Core CPU

PSoC® 63 MCUs feature a dual-core Arm® Cortex®-M4 and Cortex-M0+ architecture that allows designers to optimize for power and performance simultaneously. Using its dual cores combined with configurable memory and peripheral protection units, the PSoC® 63 MCU delivers the highest level of protection defined by the Platform Security Architecture (PSA) from Arm. Designers can use the MCU’s rich analog and digital peripherals to create custom analog front-ends (AFEs) or digital interfaces for innovative system components such as MEMS sensors and electronic-ink displays.

PSoC® 6

PSoC® 63 MCUs are part of Infineon’s PSoC® 6 scalable and reconfigurable platform architecture for a family of programmable embedded system controllers with Arm® Cortex™ CPUs (single and multi-core). The PSoC® 6 family is built on an ultra-low-power architecture, and the MCUs within it feature low-power design techniques to extend battery life up to a full week for battery powered applications.

PSoC® 63 Features

MPU Subsystem

| Bluetooth Low Energy

|

Applications

| |

PSoC® 63 Block Diagram

The block diagram shows the superset of features available in PSoC 63. Please see the datasheet for available features of dedicated devices.