FTM / Power & Power Management / Microchip — Rotary Encoder Applications

By Martin Kellermann

Business Development Manager, Microchip

How a rotary encoder works

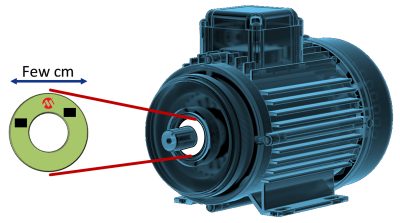

Rotary encoders are used to precisely measure the angular position of an electric motor to enable accurate control of its motion. These encoders are typically mounted on the shaft of the electric motor.

This position on the motor shaft constrains the design of the motor system in various ways:

These constraints mean that the system designer needs to select components which are reliable, produce little self-heating, and have a small footprint. In addition, as encoders are manufactured in very high volume, they have a relatively low unit cost. This means that the cost of cooling and PCB assembly have a high impact on system cost.

Another design factor which often needs to be taken into account is functional safety: this imposes a requirement to know whether measurement values are valid, or whether the system is at fault and needs to be brought into a safe state.

The diameter of the doughnut PCB can be as little as 35 mm, which limits the physical size of selected components to approximately 10 mm × 10 mm. At the same time, the encoder board can reach a continuous temperature of 95°C and, for limited periods, as high as 105°C. At these temperatures, the self-heating of electronic components attributable to leakage current can have a marked effect, even leading to thermal runaway.

SmartFusion2 SoC in the FCSG158 Package

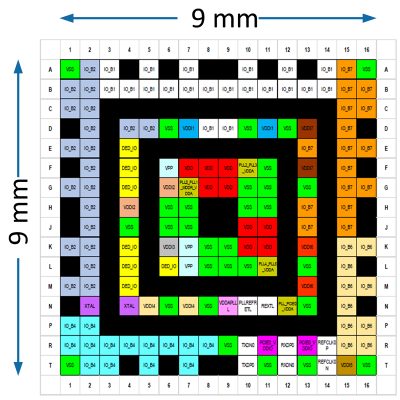

Microchip has designed a device to meet the needs of these applications: the SmartFusion®2 system-on-chip (SoC) FPGA in an FCSG158 package. This device combines an Arm® Cortex®-M3 microcontroller core, for housekeeping and communication functions, with an FPGA fabric of approximately 25,000 logic elements (LEs) in a package which has a footprint of 9 mm × 9 mm, as shown in Figure 2. This device is optimized for the harsh operating conditions and design constraints encountered in rotary encoder boards.

Because the SmartFusion2 package provides for optimized routing, the designer benefits from full break-out of the package, with only two signal layers on the PCB: this allows for the use of a simple and slim PCB. The free space in the ball-grid of the package allows the placement of cost-efficient 0.3 mm vias for the inner ring, and of decoupling capacitors directly under the package close to the supply pins in the middle of the package, shown in Figure 3.

This SmartFusion2 SoC FPGA provides 82 I/Os, 70 of which are capable of interfacing to 3.3 V. Twelve I/Os can natively interface to 2.5 V, or via resistive dividers to 3.3 V. Additionally, for situations requiring high-speed communication, one transceiver pair can run at up to 5 Gbits/s and support a PCIe Gen2 interface.

The power-optimized architecture of the SmartFusion2 produces little self-heating: this means that the device can be operated in ambient temperatures close to the maximum temperature of 125°C specified in the datasheet. Designers can calculate accurate estimations of power consumption and self-heating with the Microchip Power Estimator tool.

In safety-critical systems, the FPGA design may also require safety certification. Microchip supports this requirement with a SmartFusion2/IGLOO2 safety package. The SmartFusion2 and IGLOO®2 devices are certified for functional safety according to the IEC 61508 standard. The appropriate safety package includes the Libero® SoC 18.3 SP4 safety-certified development environment, 28 IP cores which are often required in FPGA designs, the safety manual for these devices, and utilities to calculate the probability of hardware failures.

As Microchip FPGAs and SoCs are immune to single event upsets (SEUs) on the configuration memory, permanent hardware failures are the only contributor to the failure-in-time (FIT) calculation required for safety certification. One FIT is equal to one failure in 109 hours. For typical SRAM-based FPGAs, the soft FIT caused by SEUs is dependent on the architecture and the complexity of the chosen device, and is typically around 400 FIT.

This estimate assumes that safety-relevant functionality occupies only a small fraction of the FPGA fabric. On top of this soft FIT rate, the effect of permanent failures must also be taken into account.

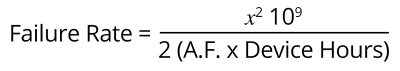

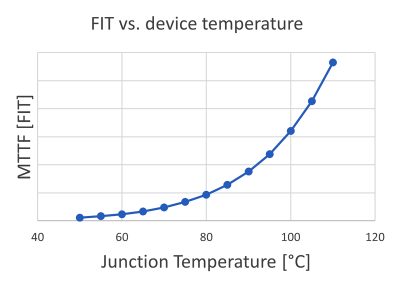

The FIT rate for permanent failures is derived from vendor measurement data at increased device stress levels, which accelerate typical aging effects. These measurement results are the basis of calculations of hardware failure rates under the desired operational conditions based on the Arrhenius relationship:

Where: A. F. is the acceleration factor

Figure 4 shows a graphical representation of this calculation.

When doing the calculation for a complete FPGA, the resulting failure rate at ambient temperatures of higher than 90°C, at which rotary encoders often operate, can reach as high as 100 FIT. For functionally safe designs, this is far too high. This means that the designer either needs to limit the device’s operating temperature, or reduce the size of the safety-relevant functionality.

The Microchip safety package contains the appropriate data and utilities to determine the FIT rate of the safety-relevant fraction of the overall design. This eases the process of certifying a design. In addition, Microchip collaborates with industry experts who can provide consultancy services for functional safety designs.

Be at the forefront of New Technology Innovations

Be at the forefront of New Technology Innovations

© 2024 Future Electronics. All rights reserved. Privacy | Terms & Conditions of Sale | Terms of Use | Accessibility