FTM / Intelligent Sensing / Future Electronics — Silicon Process Innovations for FPGAs

Future Electronics

Big, expensive FPGAs from Intel or AMD are optimized for performance, not low power. This has given rise to a general perception that FPGAs, for all the advantages of flexibility and programmable hardware configuration, require the designer to pay a price in higher power consumption, especially in comparison to microcontrollers.

In fact, FPGAs from other manufacturers, which serve the low-end and mid-range markets and provide a streamlined hardware architecture with just enough logic elements (LEs) for embedded applications, can be highly power-efficient. These FPGAs provide deterministic execution and support parallel processing, making them ideal for functions such as data translation and bridging, always-on sensor hubs, and artificial intelligence (AI) and machine learning inference at the edge.

So how is a design engineer to choose a low-end or mid-range FPGA family for a design project in which low power consumption is a highly important success factor? This is a case in which it pays to look beyond the product datasheet, and to understand the silicon architecture on which each FPGA is built.

The elements of power consumption in an FPGA

The requirement to increase power efficiency in electronics designs goes far beyond just battery-powered devices. Low-power operation and the resulting low self-heating bring multiple benefits to every electronic system, by:

A low-end or mid-range FPGA will in many cases perform the most important functions of the system, and so its power consumption is likely to be the biggest contributor to overall energy use. This means that it is important to understand how an FPGA consumes power. There are in fact two elements of FPGA power consumption: static and dynamic.

Static power is the power consumed by the FPGA when it is powered on but not actively performing any operations. This power is caused by leakage currents in the transistors and other elements of the FPGA. Static power consumption is relatively constant and does not vary much whether the FPGA is operating at full speed or in quiescent mode. Static power is directly related to the number of logic elements, the voltage of the power supply to the chip, and the chip temperature. Static power is also strongly affected by the characteristics of the silicon process technology in which the FPGA is fabricated.

Dynamic power is the power consumed by the FPGA when it is actively performing operations. This power is caused by the switching of internal capacitances in the FPGA. Dynamic power consumption is proportional to the switching activity of the FPGA. The more frequently the internal capacitances switch, the more dynamic power is consumed.

The total power consumption of an FPGA is the sum of the static power consumption and the dynamic power consumption.

Dynamic power consumption can be managed to a large extent by the system designer. Techniques such as clock gating, which avoids wasting power on unused clock tree branches, and a synthesis option for RAM implementation, which divides RAM blocks on the address width, can be applied to any type of FPGA.

Static power consumption cannot be controlled directly in the same way, although the designer can influence it through the choice of the FPGA configuration. In selecting the FPGA, for instance, the number of LEs is an important factor: there is a trade-off between density and static power consumption. Choosing an FPGA with more LEs can enable more functionality, but at the cost of higher static power consumption.

The silicon process technology of the chosen FPGA also strongly affects static power consumption, and this is different for each FPGA manufacturer. In the low-end and mid-range FPGA markets, Lattice Semiconductor and Microchip are the most prominent manufacturers: both companies have made strong but contrasting efforts to develop fabrication processes that dramatically reduce static power consumption compared to the traditional SRAM-based FPGA technology used by Intel and AMD.

A comparison of FPGA low-power silicon technologies

Microchip occupies a position in the mid-range market with its broad PolarFire® family of FPGAs: this includes the SoC PolarFire series, which features a hard-wired RISC-V CPU alongside the programmable LEs. This fabric is fundamentally different from that of a traditional SRAM-based FPGA. In a Microchip FPGA, the programmable cells are formed from a non-volatile memory technology that is similar to Flash memory, as shown in Figure 1.

Unlike SRAM-based FPGAs, this non-volatile cell technology is live at power-up, reducing system boot time. In addition, it offers power savings of between 30% and 50% compared to a typical SRAM-based FPGA.

Fig. 1: The Microchip non-volatile FPGA cell shown on the left is optimized for a balance of performance and low power consumption. The SRAM cell on the right, which draws a substantial leakage current, is optimized for high performance.

The advantage of using non-volatile cells has been strengthened with the introduction of the latest generation of Microchip FPGA technology, shown in Figure 2. The silicon-oxide-nitride-oxide-silicon (SONOS) process is made in a relatively advanced 28 nm process, providing cost and performance advantages over the 65 nm node used in the previous Microchip floating-gate technology.

The configuration of the SONOS cell is particularly well structured for low power consumption. Two programmable configurations control the FPGA data signal path. In the stack leakage path, one of the two non-volatile elements is always programmed into a very deep off-state condition. When the datapath is on, the N-channel non-volatile element is in the Off state with its voltage shifted around 0.5 V above a normal transistor voltage, meaning that the leakage current will fall to a negligible value, which is much lower than that of a standard CMOS transistor stack.

The switch leakage path, when the datapath is off, is the leakage across an Off state switch. The switch is high voltage, and has been optimized to draw much lower leakage current than a standard transistor.

Fig. 2: Cell configuration of Microchip’s SONOS FPGA technology. The configuration in the On state is shown on the left, and in the Off state on the right.

The non-volatile SONOS cell also retains its state after power has been switched off, allowing the FPGA to return to normal operation without reconfiguration. Overall, Microchip estimates that the PolarFire FPGA static power consumption is just 10% compared to that of SRAM-based FPGAs.

The non-volatile technology approach to FPGA fabrication is unique to Microchip, but the other major player in the low-end FPGA market, Lattice, has also adopted new process technology that provides for low static power consumption.

The Lattice Nexus platform FPGAs use a fully depleted silicon-on-insulator (FD-SOI) technology developed by Samsung, and which is similar to the bulk CMOS process used for fabricating the majority of semiconductors. Unlike Microchip, Lattice uses a volatile SRAM technology: a bitstream stored in an internal or external configuration memory programs the FPGA at each power-up sequence.

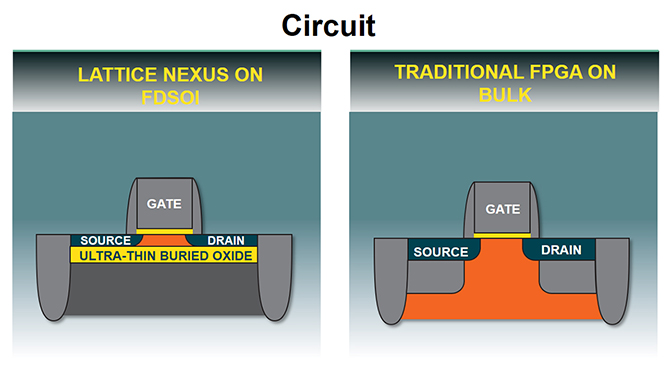

The deployment of FD-SOI technology substantially reduces leakage current from the SRAM cell compared to traditional SRAM bulk process technology. FD-SOI technology features an ultra-thin buried oxide layer which creates a very small and efficient channel. This has low parasitic capacitance and leakage current, as shown in Figure 3. In addition, the cell has a soft error rate which is typically around 100 times lower than that of bulk silicon SRAM, since the area prone to particle strikes, shown in orange in Figure 3, is much smaller.

Fig. 3: The Lattice FD-SOI technology has an ultra-thin buried oxide layer which dramatically reduces parasitic capacitance

Another advantage of the FD-SOI technology is the scope to control body bias to tune the FPGA for either low power or high performance. A bulk resistor which sits on the body of the transistor enables the developer to control the strength of the transistor during operation. Control of the body bias, which is programmable via the Lattice development environment, gives the choice of either a high-performance mode or a low-power mode depending on the power and thermal constraints of the application.

Lattice estimates that FPGAs manufactured on the Nexus FD-SOI platform offer power consumption as much as 75% lower than competing FPGAs of a similar class.

How to take static power consumption into account in FPGA selection

The effect of process technology on the choice of FPGA must be put into perspective: power is only part of the classic power/performance/area/cost (PPAC) set of trade-offs in electronics design. Static power consumption is only one element of the power equation, and dynamic power is a greater portion of total power consumption than static power.

Nevertheless, the innovations that Microchip and Lattice have introduced in the FPGA fabrication process provide substantial static power savings, and reinforce the attractiveness of low-end and mid-range FPGAs for use in AI-based and many other applications.

Be at the forefront of New Technology Innovations

Be at the forefront of New Technology Innovations

© 2024 Future Electronics. All rights reserved. Privacy | Terms & Conditions of Sale | Terms of Use | Accessibility